Contador de cuenta arbitraria de 4 bits que realice la cuenta de 8 números diferentes en este orden:

2 - 4 - 6 - 14 - 0 - 15 - 7 - 5

Lo tengo que hacer en VERILOG.

He realizado lo siguiente:

o 1. Diagrama de estados

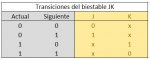

o 2. Tabla de transiciones del biestable JK

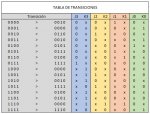

o 3. Tabla de transiciones completa

o 4. Mapas de Karnaugh con las ecuaciones

(Dejo adjunto los cuatro archivos)

Además os dejo un circuito hecho, pero no se que tengo que modificar.

2 - 4 - 6 - 14 - 0 - 15 - 7 - 5

Lo tengo que hacer en VERILOG.

He realizado lo siguiente:

o 1. Diagrama de estados

o 2. Tabla de transiciones del biestable JK

o 3. Tabla de transiciones completa

o 4. Mapas de Karnaugh con las ecuaciones

(Dejo adjunto los cuatro archivos)

Además os dejo un circuito hecho, pero no se que tengo que modificar.

PHP:

//Modulo del biestable JK

module JKdown(output reg Q, output wire NQ, input wire J, input wire K, input wire C);

not(NQ,Q);

initial

begin

Q=0;

end

always @(posedge C)

case ({J,K})

2'b10: Q=1;

2'b01: Q=0;

2'b11: Q=~Q;

endcase

endmodule

//Módulo que contiene el contador y la circuitería auxiliar.

module contador (output wire [3:0] Q, input wire C);

//Cables correspondientes a las salidas negadas de los biestables.

wire [3:0] nQ;

//Cables que almacenan la salida temporal del biestable jk3.

wire Qt, nQt;

//Cables de entrada a los biestables.

wire wJ3, wJ2, wJ1, wK0;

//Cables intermedios.

wire wn0n1, wq0q1, wn0q3, wn3n1, wq2q3;

//Puertas correspondientes al contador.

and n0n1 (wn0n1, nQ[0], nQ[1]);

or J3 (wJ3, wn0n1, Q[2]);

and q0q1 ( wq0q1, Q[0], Q[1]);

and n0q3 ( wn0q3, nQ[0], Qt);

or J2 (wJ2, wq0q1, wn0q3);

and J1 (wJ1, nQ[2], nQt, Q[0]);

and n3n1 (wn3n1, nQt, nQ[1]);

or K0 (wK0, wn3n1, Q[2]);

JKdown jk1 (Q[0], nQ[0], 1'b1, wK0, C);

JKdown jk2 (Q[1], nQ[1], wJ1, Q[0], C);

JKdown jk3 (Q[2], nQ[2], wJ2, 1'b1, C);

JKdown jk4 (Qt, nQt, wJ3, Q[0], C);

//Circuitería adicional que cambia el nueve por el uno.

and q2q3 (wq2q3, Q[2], Qt);

or NQ3 (Q[3], wq2q3, wn0q3);

endmodule

//Módulo para probar el circuíto.

module test;

reg I, C;

wire [3:0] Q;

contador counter (Q,C);

always

begin

#10 C=~C;

end

initial

begin

$dumpfile("ej1_34-5.dmp");

$dumpvars(2, counter, Q);

C=0;

#500 $finish;

end

endmodule