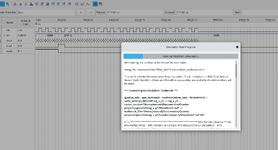

Hola con todos, tengo instalado Quartus en debian, y al momento de simular en "University Program VWF" se queda estancado y no termina el proceso. La verdad no tengo ni idea de como solucionar

Determining the location of the ModelSim executable...

Using: /home/manuel/intelFPGA_lite/19.1/modelsim_ae/linuxaloem/

To specify a ModelSim executable directory, select: Tools -> Options -> EDA Tool Options

Note: if both ModelSim-Altera and ModelSim executables are available, ModelSim-Altera will be used.

**** Generating the ModelSim Testbench ****

quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off reg_s_p1 -c reg_s_p1 --vector_source="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/Waveform7.vwf" --testbench_file="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/Waveform7.vwf.vht"

Info: *******************************************************************Info: Running Quartus Prime EDA Netlist Writer Info: Version 19.1.0 Build 670 09/22/2019 SJ Lite Edition Info: Copyright (C) 2019 Intel Corporation. All rights reserved. Info: Your use of Intel Corporation's design tools, logic functions Info: and other software and tools, and any partner logic Info: functions, and any output files from any of the foregoing Info: (including device programming or simulation files), and any Info: associated documentation or information are expressly subject Info: to the terms and conditions of the Intel Program License Info: Subscription Agreement, the Intel Quartus Prime License Agreement, Info: the Intel FPGA IP License Agreement, or other applicable license Info: agreement, including, without limitation, that your use is for Info: the sole purpose of programming logic devices manufactured by Info: Intel and sold by Intel or its authorized distributors. Please Info: refer to the applicable agreement for further details, at Info: FPGA Software Download Center. Info: Processing started: Mon Mar 18 01:01:27 2024Info: Command: quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off reg_s_p1 -c reg_s_p1 --vector_source="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/Waveform7.vwf" --testbench_file="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/Waveform7.vwf.vht"Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.

Completed successfully.

**** Generating the functional simulation netlist ****

quartus_eda --write_settings_files=off --simulation --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/" reg_s_p1 -c reg_s_p1

Info: *******************************************************************Info: Running Quartus Prime EDA Netlist Writer Info: Version 19.1.0 Build 670 09/22/2019 SJ Lite Edition Info: Copyright (C) 2019 Intel Corporation. All rights reserved. Info: Your use of Intel Corporation's design tools, logic functions Info: and other software and tools, and any partner logic Info: functions, and any output files from any of the foregoing Info: (including device programming or simulation files), and any Info: associated documentation or information are expressly subject Info: to the terms and conditions of the Intel Program License Info: Subscription Agreement, the Intel Quartus Prime License Agreement, Info: the Intel FPGA IP License Agreement, or other applicable license Info: agreement, including, without limitation, that your use is for Info: the sole purpose of programming logic devices manufactured by Info: Intel and sold by Intel or its authorized distributors. Please Info: refer to the applicable agreement for further details, at Info: FPGA Software Download Center. Info: Processing started: Mon Mar 18 01:01:28 2024Info: Command: quartus_eda --write_settings_files=off --simulation=on --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/" reg_s_p1 -c reg_s_p1Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.Info (204019): Generated file reg_s_p1.vho in folder "/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim//" for EDA simulation toolInfo: Quartus Prime EDA Netlist Writer was successful. 0 errors, 1 warning Info: Peak virtual memory: 1101 megabytes Info: Processing ended: Mon Mar 18 01:01:28 2024 Info: Elapsed time: 00:00:00 Info: Total CPU time (on all processors): 00:00:00

Completed successfully.

**** Generating the ModelSim .do script ****

/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/reg_s_p1.do generated.

Completed successfully.

**** Running the ModelSim simulation ****

/home/manuel/intelFPGA_lite/19.1/modelsim_ae/linuxaloem//vsim -c -do reg_s_p1.do

Determining the location of the ModelSim executable...

Using: /home/manuel/intelFPGA_lite/19.1/modelsim_ae/linuxaloem/

To specify a ModelSim executable directory, select: Tools -> Options -> EDA Tool Options

Note: if both ModelSim-Altera and ModelSim executables are available, ModelSim-Altera will be used.

**** Generating the ModelSim Testbench ****

quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off reg_s_p1 -c reg_s_p1 --vector_source="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/Waveform7.vwf" --testbench_file="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/Waveform7.vwf.vht"

Info: *******************************************************************Info: Running Quartus Prime EDA Netlist Writer Info: Version 19.1.0 Build 670 09/22/2019 SJ Lite Edition Info: Copyright (C) 2019 Intel Corporation. All rights reserved. Info: Your use of Intel Corporation's design tools, logic functions Info: and other software and tools, and any partner logic Info: functions, and any output files from any of the foregoing Info: (including device programming or simulation files), and any Info: associated documentation or information are expressly subject Info: to the terms and conditions of the Intel Program License Info: Subscription Agreement, the Intel Quartus Prime License Agreement, Info: the Intel FPGA IP License Agreement, or other applicable license Info: agreement, including, without limitation, that your use is for Info: the sole purpose of programming logic devices manufactured by Info: Intel and sold by Intel or its authorized distributors. Please Info: refer to the applicable agreement for further details, at Info: FPGA Software Download Center. Info: Processing started: Mon Mar 18 01:01:27 2024Info: Command: quartus_eda --gen_testbench --tool=modelsim_oem --format=vhdl --write_settings_files=off reg_s_p1 -c reg_s_p1 --vector_source="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/Waveform7.vwf" --testbench_file="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/Waveform7.vwf.vht"Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.

Completed successfully.

**** Generating the functional simulation netlist ****

quartus_eda --write_settings_files=off --simulation --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/" reg_s_p1 -c reg_s_p1

Info: *******************************************************************Info: Running Quartus Prime EDA Netlist Writer Info: Version 19.1.0 Build 670 09/22/2019 SJ Lite Edition Info: Copyright (C) 2019 Intel Corporation. All rights reserved. Info: Your use of Intel Corporation's design tools, logic functions Info: and other software and tools, and any partner logic Info: functions, and any output files from any of the foregoing Info: (including device programming or simulation files), and any Info: associated documentation or information are expressly subject Info: to the terms and conditions of the Intel Program License Info: Subscription Agreement, the Intel Quartus Prime License Agreement, Info: the Intel FPGA IP License Agreement, or other applicable license Info: agreement, including, without limitation, that your use is for Info: the sole purpose of programming logic devices manufactured by Info: Intel and sold by Intel or its authorized distributors. Please Info: refer to the applicable agreement for further details, at Info: FPGA Software Download Center. Info: Processing started: Mon Mar 18 01:01:28 2024Info: Command: quartus_eda --write_settings_files=off --simulation=on --functional=on --flatten_buses=off --tool=modelsim_oem --format=vhdl --output_directory="/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/" reg_s_p1 -c reg_s_p1Warning (18236): Number of processors has not been specified which may cause overloading on shared machines. Set the global assignment NUM_PARALLEL_PROCESSORS in your QSF to an appropriate value for best performance.Info (204019): Generated file reg_s_p1.vho in folder "/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim//" for EDA simulation toolInfo: Quartus Prime EDA Netlist Writer was successful. 0 errors, 1 warning Info: Peak virtual memory: 1101 megabytes Info: Processing ended: Mon Mar 18 01:01:28 2024 Info: Elapsed time: 00:00:00 Info: Total CPU time (on all processors): 00:00:00

Completed successfully.

**** Generating the ModelSim .do script ****

/home/manuel/Documentos/Quartus projects/ejemplo2/reg_s_p1/simulation/qsim/reg_s_p1.do generated.

Completed successfully.

**** Running the ModelSim simulation ****

/home/manuel/intelFPGA_lite/19.1/modelsim_ae/linuxaloem//vsim -c -do reg_s_p1.do