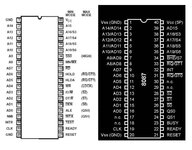

Aqui les muestro como quedaria la tarjeta principal definitiva para la CPU 8088 , como se puede apreciar en esta placa esta solo los componentes concernientes a darle soporte al CPU como es principalmente el generador de señal de clock , reset y ready en el chip 82C84, para este microprocesador se recomienda que la señal de reloj tenga un ciclo alto de 33% y bajo de %66 que justo se lo provee ese chip generador de reloj, desde que hize mi primera tarjeta no le llegue a probar con un oscilador de reloj a base de inversores como se da para el Z80 asi que no sabria si realmente corre bien con ello o se entorpece al funcionar y que sea imprescindible el uso del 82C84, que aun se puede conseguir de tarjetas viejas o pidiendolo online a tiendas chinas que deberian vender el conjunto completo pero sin embargo estan desperdigados por varias tiendas para juntar los componentes , bueno pero tambien hare una prueba de si el CPU corre con un oscilador de inversores o si trabaja tambien con un oscilador integrado de 4 pines y entonces le hare una version de esta misma tarjeta solo cambiando el circuito de reloj , reset y ready ,manteniendose todo lo demas igual , eso seria para el caso si no se puedan conseguirse el 82C84, pues no puedes comprarte en tienda online uno sino un lote de 5 a 10 unidades minimo.

Para el bus de datos tenemos el buffer 74LS245 que es un buffer bidireccional controlado por dos pines del CPU que son /DEN y DT/-R, en los diagramas habituales del circuito para el CPU 8088 solian incluir siempre latch 74LS373 que debido a que sus pines son entreverados uno opta por su version emparejada 74LS573, pero recuerdo que incluso usando estos integrados tenia problemas para la estabilidad en el bus de direcciones de un 8085 donde uno ve un 74LS373 al que le llega a travez de un inversor la señal ALE, pero por alguna razon no me funcionaba bien y opte por seguir usando ese inversor pero cambie los 74LS573 de nivel alto por los 74LS574 de flanco de subida y me trabajo bien , por eso en este circuito he acondicionado un 74LS04 inversor para el caso no vaya bien los 74LS573 o no se disponga de ellos y se use dos latch 74LS574 , de alli que si no requiere inversor pues se quita el 74LS04 y se puentea sus pines 1 y 2 de tal modo:

- si uso dos latch por nivel alto 74LS573 quito el 74LS04 y puenteo sus pines 1 y 2 en el impreso (se puede habilitar un jumper tambien)

- si uso dos latch por flanco alto 74LS574 coloco el 74LS04 y que trabaje el primer inversor

como las señales INTR , NMI y RDY son activo alto se requiere mantenerlos a nivel bajo a travez de resistencias de 3.3K u otro valores proximos , dos de ellas se pueden apreciar cerca al Micro para INTR y NMI mientras que las dos para RDY 1 y RDY2 se colocan entre esos par de dos puntos verticales que estan en la parte inferior izquierda junto al conector de la tarjeta de soporte de memoria y perifericos, de ese modo al no usar esos terminales les estara llegando un nivel bajo por las resistencias de 3.3K y no se dispararan

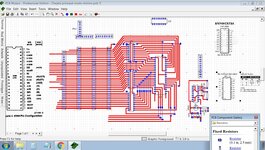

Y entonces esta seria la tarjeta de soporte de memoria y perifericos , el lado derecho es el que se conecta a la tarjeta del CPU mediante espadines correspondientes Hembra y Macho, se daran cuenta que podria tambien uno preparar el circuito completo de una sola pieza pero seria un poco grande como para meterlo en un recipiente para el ataque del acido si lo hace uno mismo , asi que he preferido cortarlo en dos partes para mas comodidad.

Como se menciono antes los 3 zocalos destinados a soportar la memoria RAM y ROM no tienen un decodificador que genere la seleccion de los chips de memoria (como el modulo del Z80 ) pues tenemos el bus completo de 20 bits alli presente, la decodificacion del mapeo de memoria se tiene que hacer en cada modulo de memoria individual , por ejemplo si quiero usar una Eeprom de 32 Kbytes le tengo que agregar su integrado decodificador o compuertas para seleccionar que se active y cubra la parte alta 0FFFF0H en donde se situa posterior al reseteo mientras que si coloco una RAM tengo que ubicarla en el mapa de memoria en la parte baja empezando en la direccion 0000H hasta donde de la capacidad de memoria. por ejemplo si quisiera dividir el area de 1 mega en dos simplemente colocaria una compuerta OR entre la señal A19 e IO/-M para activarla cuando ambas señales esten a nivel bajo y para la Eeprom le colocaria tambien una compuerta OR pero al A19 lo antecederia por un inversor y con ello se me activa en la parte alta , pero como es mas posible tener memorias RAM de capacidad pequeña como 32K, 64K y 128K entonces se le adiciono un tercer slot para agregarle mas RAM , por ejemplo una configuracion seria de

- 32 Kbyte ROM + 128 Kbyte RAM + 128 Kbyte RAM o

- 64 Kbyte ROM + 32 Kbyte ROM + 512 Kbyte RAM, (esta ultima seria casi como en los requerimientos del amigo Antiworldx que dio inicio a este post sobre miniordenador con 8088)

para configuraciones mas rebuscadas tedriamos que usar hasta circuitos GAL pero yo creo que con lo basico es suficiente para el estudio, practicas con este CPU que muchos tenemos en nuestras alacenas mirandonos de reojo , yo creo que tengo como una veintena de los antiguos de 4.77 mhz y un par que trabaja a 10 Mhz

En la parte del medio de esta tarjeta tambien podemos apreciar que si se a incluido un decodificador 74LS138 para los perifericos al cual le llegan las señales del bus A11...A15 mas la señal IO/-M ,a nivel bajo slecciona memoria y a nivel alto selecciona perifericos , de alli tenemos 5 señales de seleccion desde /CS0..../CS4 con lo que cubrimos uno para cada slot disponible, al igual que para el Z80 tendremos los siguientes modulos standar como con un PPI, un USART o ACIA, un ADC con o sin DAC, UN PTC o dos , un PIC para gestionar las interrupciones vectorizadas y por ultimo un modulo I2C donde podamos tener un DS1307 y una memoria 24C256 para guardar un programa desde la RAM y volverlo a restaurar al encender el sistema, en esta parte me voy a romper la cabeza que quizas termine usando un microcontrolador de apoyo para esta tarea de gestionar el bus I2C que hasta podria ser un par de de ellos para conectar dispositivos I2C variados como por ejemplo un pantalla LCD 16x2 o 20x4 que tengan modulo I2C..

la señal IO/-M tambien persiste en el bus hacia los perifericos porque esta sera usada para un circuito de estados de espera wait que se activara cuando el bus del sistema principal este corriendo a 8 u 10 Mhz posibles mientras que los perifericos que suelen correr del orden de 2 a 5 mhz requieran agregar unos estados de espera por ser mas lentos.

Antes de estar disponibles las mascaras en PCBwizard (salvo alguien las quiera probar ya) tendre que construirlo para someterlo a las pruebas de funcionamiento y darle su visto bueno por si hubiera algun error que se me a pasado y corregirlo para que otros hobbistas lo armen sin problema jeje

Lo siguiente para echarla a funcionar es completar los 2 modulos de memoria RAM y ROM basicos y su modulo ACIA 68B50 que funcionara tal como en el modulo para Z80