Hola, otra manera más eficiente, pero también más complejo, es hacer un divisor cómo el que plantee, pero de aproximación sucesiva.

Es decir volvemos al ejem. inicial.

Queremos dividir 10 entre 3

Entonces, habilitamos el bit más ponderante del divisor 1000.

Multiplicamos 1000*0011=desborde.

Ahora multiplicamos 0100*0011=desborde.

Luego multiplicamos 0010*0011=menor que diez.

Aquí mantenemos el bit en alto porque la comprobación es menor y por último probamos con el bit menor.

0011*0011= menor que diez.

En conclusión, el sistema va, probando del bit de mayor peso hacia el menor. Es decir en cuatro pasos se alcanza el valor más próximo.

Si, luego de que se comprueba que el resultado es menor, entonces ese bit se mantiene en alto y se continúa la selección bit a bit hacia el menor peso.

Aclarando aún más

(A) sería ntro. divisor.

(B) Ntro. dividendo.

(X) valor 0 o 1 según comprobación.

1er. Paso 1000*(A) < B

2do. Paso X100*(A) " " "

3er. Paso XX10*(A) " " "

4to. Paso XXX1*(A) " " "

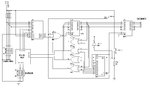

Cómo generar la lógica?

Puede hacerse con un latch D de cuatro bits con el agregado de compuertas OR en su entrada y a su salida. Luego con un secuenciador tipo 4017, generar el barrido de bits del mayor al menor.

Ésto lo implemente una vez en un ADC de 16 bits para digitalizar audio.

Es decir volvemos al ejem. inicial.

Queremos dividir 10 entre 3

Entonces, habilitamos el bit más ponderante del divisor 1000.

Multiplicamos 1000*0011=desborde.

Ahora multiplicamos 0100*0011=desborde.

Luego multiplicamos 0010*0011=menor que diez.

Aquí mantenemos el bit en alto porque la comprobación es menor y por último probamos con el bit menor.

0011*0011= menor que diez.

En conclusión, el sistema va, probando del bit de mayor peso hacia el menor. Es decir en cuatro pasos se alcanza el valor más próximo.

Si, luego de que se comprueba que el resultado es menor, entonces ese bit se mantiene en alto y se continúa la selección bit a bit hacia el menor peso.

Aclarando aún más

(A) sería ntro. divisor.

(B) Ntro. dividendo.

(X) valor 0 o 1 según comprobación.

1er. Paso 1000*(A) < B

2do. Paso X100*(A) " " "

3er. Paso XX10*(A) " " "

4to. Paso XXX1*(A) " " "

Cómo generar la lógica?

Puede hacerse con un latch D de cuatro bits con el agregado de compuertas OR en su entrada y a su salida. Luego con un secuenciador tipo 4017, generar el barrido de bits del mayor al menor.

Ésto lo implemente una vez en un ADC de 16 bits para digitalizar audio.

Última edición: