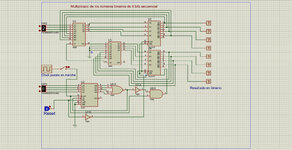

Este proyecto está orientado a realizar una calculadora con circuitos lógicos, como el integrado 74LS284 y 74LS285 han dejado de fabricarse, que son multiplicadores binarios de 4 bits, he diseñado este circuitos con sumadores en cascada, flip-flop tipo D síncrono, y un contador binario,

El truco está en programar el contador en descendente cargando el inicio con el numero binario multiplicador, cuando llega a cero queda paralizado el contador a través de una NOR cuádruple, que conecta con el ENABLE del contador. De esta manera los sumadores se recargarán tantas veces como el contador permita el Clock, que dispara a los flip-flop D, o sea permite que los sumadores vayan sumando tantas veces como el número binario multiplicador prefijado. Hay que tener en cuenta que cuando el primer sumador se desborde, activará el carry de salida, que corresponderá al número decimal 16, esto será el número más bajo del segundo sumador, y como el primer sumador también se realimenta a través de los flip-flop D síncrono, sus salidas serán=16, 32, 64 y 128, mientras evidentemente el CI flip flop D que realimenta el primer contador, su salida serán=1, 2, 4 y 8. La puerta AND que figura está para desactiva el Clock sobre los flip flop cuando la cuenta del contador está a cero, ya ha acabado de calcular la multiplicación.

Si alguien la quiere probar aquí la adjunto en fichero Proteus 8

El truco está en programar el contador en descendente cargando el inicio con el numero binario multiplicador, cuando llega a cero queda paralizado el contador a través de una NOR cuádruple, que conecta con el ENABLE del contador. De esta manera los sumadores se recargarán tantas veces como el contador permita el Clock, que dispara a los flip-flop D, o sea permite que los sumadores vayan sumando tantas veces como el número binario multiplicador prefijado. Hay que tener en cuenta que cuando el primer sumador se desborde, activará el carry de salida, que corresponderá al número decimal 16, esto será el número más bajo del segundo sumador, y como el primer sumador también se realimenta a través de los flip-flop D síncrono, sus salidas serán=16, 32, 64 y 128, mientras evidentemente el CI flip flop D que realimenta el primer contador, su salida serán=1, 2, 4 y 8. La puerta AND que figura está para desactiva el Clock sobre los flip flop cuando la cuenta del contador está a cero, ya ha acabado de calcular la multiplicación.

Si alguien la quiere probar aquí la adjunto en fichero Proteus 8

Adjuntos

Última edición: